### **Features**

- Operating Voltage: 3.3VAccess Time: 40 ns

- Very Low Power Consumption

- Active: 160 mW (Max)Standby: 70 µW (Typ)

- Wide Temperature Range: -55°C to +125°C

- MFP 32 leads 400 Mils Width Package

- TTL Compatible Inputs and Outputs

- Asynchronous

- Designed on 0.35µm Process

- No Single Event Latch-up below a LET threshold of 80 MeV/mg/cm<sup>2</sup>

- Tested up to a Total Dose of 200 Krad (Si) according to MIL STD 883 Method 1019

- Quality grades: QML Q or V with SMD 5962-02501

# **Description**

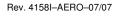

The M65609E is a very low power CMOS static RAM organized as 131,072 x 8 bits. Utilizing an array of six transistors (6T) memory cells, the M65609E combines an extremely low standby supply current with a fast access time at 40 ns. The high stability of the 6T cell provides excellent protection against soft errors due to noise.

The M65609E is processed according to the methods of the latest revision of the MIL PRF 38535 and ESCC 9000.

It is produced on the same process as the MH1RT sea of gates series.

Rad Hard 128K x 8 3.3-volt Very Low Power CMOS SRAM

M65609E

# **Block Diagram**

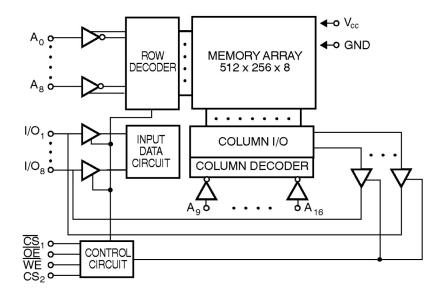

# **Pin Configuration**

# **Pin Description**

| Name            | Description       |

|-----------------|-------------------|

| A0 - A16        | Address Inputs    |

| I/O1 - I/O8     | Data Input/Output |

| CS₁             | Chip Select 1     |

| CS <sub>2</sub> | Chip Select 2     |

| WE              | Write Enable      |

| OE              | Output Enable     |

| V <sub>CC</sub> | Power             |

| GND             | Ground            |

Table 1. Truth Table

| CS₁ | CS <sub>2</sub> | WE | ŌĒ | Inputs/<br>Outputs | Mode                    |

|-----|-----------------|----|----|--------------------|-------------------------|

| Н   | Х               | Х  | Х  | Z                  | Deselect/<br>Power-down |

| Х   | L               | Х  | Х  | Z                  | Deselect/<br>Power-down |

| L   | Н               | Н  | L  | Data Out           | Read                    |

| L   | Н               | L  | Х  | Data In            | Write                   |

| L   | Н               | Н  | Н  | Z                  | Output<br>Disable       |

Note: L = low, H = high, X = H or L, Z = high impedance.

# **Electrical Characteristics**

# **Absolute Maximum Ratings**

| Supply Voltage to GND Potential0.5V + 5V                         |

|------------------------------------------------------------------|

| DC Input Voltage GND - 0.3V to V <sub>CC</sub> + 0.3V            |

| DC Output Voltage High Z State GND - 0.3V to $V_{\rm CC}$ + 0.3V |

| Storage Temperature65°C to + 150°C                               |

| Output Current Into Outputs (Low)                                |

| Electro Statics Discharge Voltage > 500V                         |

| (MIL STD 883D Method 3015.3)                                     |

\*NOTE:

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **Military Operating Range**

| Operating Voltage | Operating Temperature |

|-------------------|-----------------------|

| $3.3V \pm 0.3V$   | -55°C to + 125°C      |

# **Recommended DC Operating Conditions**

| Parameter       | Description        | Min       | Тур | Max                   | Unit |

|-----------------|--------------------|-----------|-----|-----------------------|------|

| V <sub>CC</sub> | Supply voltage     | 3         | 3.3 | 3.6                   | V    |

| Gnd             | Ground             | 0.0       | 0.0 | 0.0                   | V    |

| V <sub>IL</sub> | Input low voltage  | GND - 0.3 | 0.0 | 8.0                   | V    |

| V <sub>IH</sub> | Input high voltage | 2.2       | -   | V <sub>CC</sub> + 0.3 | V    |

# Capacitance

| Parameter                       | Description         | Min | Тур | Max | Unit |

|---------------------------------|---------------------|-----|-----|-----|------|

| C <sub>IN</sub> <sup>(1)</sup>  | Input low voltage   | -   | _   | 8   | pF   |

| C <sub>OUT</sub> <sup>(1)</sup> | Output high voltage | _   | _   | 8   | pF   |

Note: 1. Guaranteed but not tested.

## **DC Parameters**

### **DC Test Conditions**

| Parameter          | Description            | Minimum | Typical | Maximum | Unit |

|--------------------|------------------------|---------|---------|---------|------|

| IIX <sup>(1)</sup> | Input leakage current  | -1      | _       | 1       | μΑ   |

| IOZ (1)            | Output leakage current | -1      | _       | 1       | μΑ   |

| VOL (2)            | Output low voltage     | -       | _       | 0.4     | V    |

| VOH (3)            | Output high voltage    | 2.4     | _       | _       | V    |

- $\begin{aligned} &\text{Gnd} < \text{Vin} < V_{CC}, \, \text{Gnd} < \text{Vout} < V_{CC} \, \text{Output Disabled}. \\ &V_{CC} \, \text{min. IOL} = 4 \, \text{mA}. \\ &V_{CC} \, \text{min. IOH} = -2 \, \text{mA}. \end{aligned}$

- 2.

- 3.

## Consumption

| Symbol                 | Description               | 65609E-40 | Unit | Value |

|------------------------|---------------------------|-----------|------|-------|

| ICCSB (1)              | Standby supply current    | 1.5       | mA   | max   |

| ICCSB <sub>1</sub> (2) | Standby supply current    | 1         | mA   | max   |

| ICCOP (3)              | Dynamic operating current | 45        | mA   | max   |

- 1.

- 2.

- $$\label{eq:control_control_control} \begin{split} \overline{\underline{CS}}_1 &\geq \text{VIH or } CS_2 \leq \text{VIL and } \overline{CS}_1 \leq \text{VIL}. \\ \overline{CS}_1 &\geq V_{CC} \text{ } 0.3 \text{V or, } CS_2 \leq \underline{\text{Gnd}} + 0.3 \text{V and } \overline{\text{CS}}_1 \leq 0.2 \text{V} \\ F &= 1/T_{\text{AVAV}}, \, I_{\text{OUT}} = 0 \text{ mA}, \, \overline{W} = \overline{\text{OE}} = \text{VIH, Vin} = \text{Gnd or } V_{CC}, \, V_{CC} \text{ max}. \end{split}$$

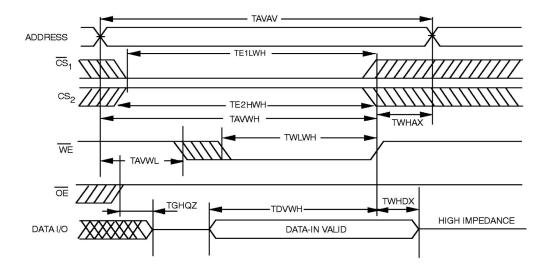

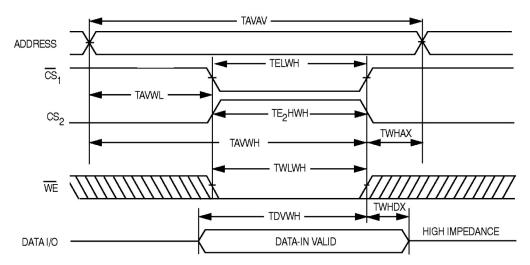

# **Write Cycle**

| Symbol             | Parameter                         | 65609E-40 | Unit | Value |

|--------------------|-----------------------------------|-----------|------|-------|

| t <sub>AVAW</sub>  | Write cycle time                  | 35        | ns   | min   |

| t <sub>AVWL</sub>  | Address set-up time               | 0         | ns   | min   |

| t <sub>AVWH</sub>  | Address valid to end of write     | 28        | ns   | min   |

| t <sub>DVWH</sub>  | Data set-up time                  | 18        | ns   | min   |

| t <sub>E1LWH</sub> | CS₁ low to write end              | 28        | ns   | min   |

| t <sub>E2HWH</sub> | CS <sub>2</sub> high to write end | 28        | ns   | min   |

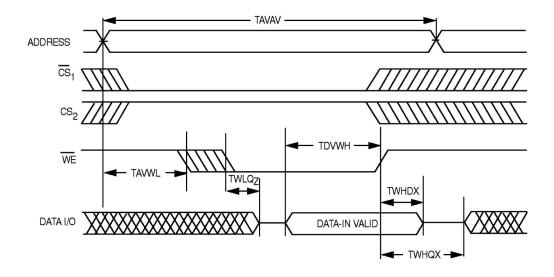

| t <sub>WLQZ</sub>  | Write low to high Z (1)           | 15        | ns   | max   |

| t <sub>WLWH</sub>  | Write pulse width                 | 28        | ns   | min   |

| t <sub>WHAX</sub>  | Address hold from to end of write | 3         | ns   | min   |

| t <sub>WHDX</sub>  | Data hold time                    | 0         | ns   | min   |

| t <sub>WHQX</sub>  | Write high to low Z (1)           | 0         | ns   | min   |

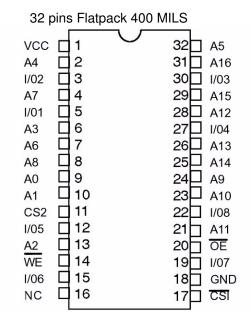

Note: 1. Parameters guaranteed, not tested, with 5 pF output loading (see Section "AC Test Conditions" Figure 2).

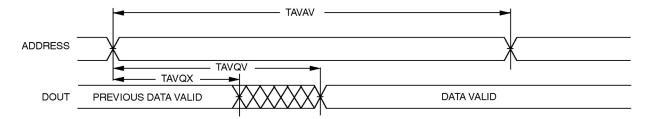

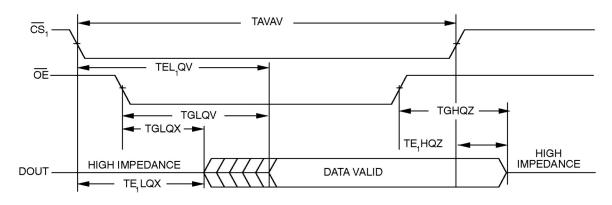

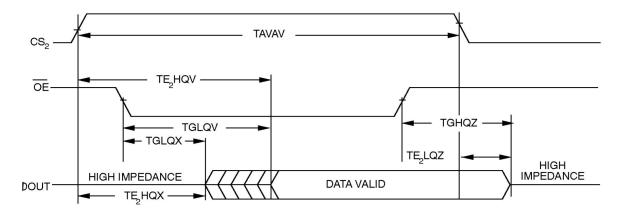

# **Read Cycle**

| Symbol             | Parameter                                            | 65609E-40 | Unit | Value |

|--------------------|------------------------------------------------------|-----------|------|-------|

| t <sub>AVAV</sub>  | Read cycle time                                      | 40        | ns   | min   |

| t <sub>AVQV</sub>  | Address access time                                  | 40        | ns   | max   |

| t <sub>AVQX</sub>  | Address valid to low Z                               | 3         | ns   | min   |

| t <sub>E1LQV</sub> | Chip-select <sub>1</sub> access time                 | 40        | ns   | max   |

| t <sub>E1LQX</sub> | $\overline{\text{CS}}_1$ low to low Z <sup>(1)</sup> | 3         | ns   | min   |

| t <sub>E1HQZ</sub> | CS <sub>1</sub> high to high Z <sup>(1)</sup>        | 15        | ns   | max   |

| t <sub>E2HQV</sub> | Chip-select <sub>2</sub> access time                 | 40        | ns   | max   |

| t <sub>E2HQX</sub> | CS <sub>2</sub> high to low Z <sup>(1)</sup>         | 3         | ns   | min   |

| t <sub>E2LQZ</sub> | CS <sub>2</sub> low to high Z <sup>(1)</sup>         | 15        | ns   | max   |

| t <sub>GLQV</sub>  | Output Enable access time                            | 12        | ns   | max   |

| t <sub>GLQX</sub>  | OE low to low Z (1)                                  | 0         | ns   | min   |

| t <sub>GHQZ</sub>  | OE high to high Z (1)                                | 10        | ns   | max   |

Note: 1. Parameters guaranteed, not tested, with 5 pF output loading (seeSection "AC Test Conditions" Figure 2).

### **AC Parameters**

### **AC Test Conditions**

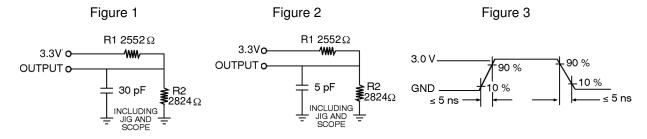

### **AC Test Loads Waveforms**

Equivalent to: THEVENIN EQUIVALENT

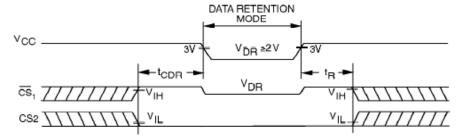

### **Data Retention Mode**

Atmel CMOS RAM's are designed with battery backup in mind. Data retention voltage and supply current are guaranteed over temperature. The following rules ensure data retention:

- 1. During data retention  $\overline{\text{CS1}}$  must be held high within  $V_{\text{CC}}$  to  $V_{\text{CC}}$  0.2V or chip select  $\overline{\text{CS2}}$  must be held down within GND to GND +0.2V.

- 2. Output Enable (OE) should be held high to keep the RAM outputs high impedance, minimizing power dissipation.

- 3. During power-up and power-down transitions  $\overline{CS1}$  and  $\overline{OE}$  must be kept between V<sub>CC</sub> + 0.3V and 70% of V<sub>CC</sub>, or with BS between GND and GND -0.3V.

- 4. The RAM can begin operation  $> t_R$  ns after  $V_{CC}$  reaches the minimum operation voltages (3V).

Figure 1. Data Retention Timing

### **Data Retention Characteristics**

| Parameter                         | Description                          | Min                              | Typical T <sub>A</sub> = 25°C | Max | Unit |

|-----------------------------------|--------------------------------------|----------------------------------|-------------------------------|-----|------|

| V <sub>CCDR</sub>                 | V <sub>CC</sub> for data retention   | 2.0                              | -                             | -   | V    |

| T <sub>CDR</sub>                  | Chip deselect to data retention time | 0.0                              | -                             | -   | ns   |

| t <sub>R</sub>                    | Operation recovery time              | t <sub>AVAV</sub> <sup>(1)</sup> | -                             | -   | ns   |

| I <sub>CCDR1</sub> <sup>(2)</sup> | Data retention current at 2.0V       | -                                | 0.010                         | 1.0 | mA   |

Notes: 1. TAVAV = Read Cycle Time

2.  $\overline{CS1} = V_{CC}$  or  $CS2 = \overline{CS1} = GND$ ,  $V_{IN} = GND/V_{CC}$ .

# Write Cycle 1. WE Controlled. OE High During Write

# $\underline{\underline{Wr}}$ ite Cycle 2. $\overline{\underline{WE}}$ Controlled. OE Low

# Write Cycle 3. CS1 or CS2 Controlled<sup>(1)</sup>

Note: 1. The internal write time of the memory is defined by the overlap of  $\overline{CS1}$  LOW and CS2 HIGH and  $\overline{W}$  LOW. Both signals must be activated to initiate a write and either signal can terminate a write by going in activated. The data input setup and hold timing should be referenced to the actived edge of the signal that terminates the write. Data out is high impedance if  $\overline{OE} = V_{IH}$ .

# Read Cycle nb 1

# Read Cycle nb 2

# Read Cycle nb 3

# **Ordering Information**

| Part Number                      | Temperature Range | Speed | Package | Flow                |

|----------------------------------|-------------------|-------|---------|---------------------|

| MMDJ-65609EV-40-E                | 25°C              | 40 ns | FP32.4  | Engineering Samples |

| 5962-0250101QXC                  | -55 to +125°C     | 40 ns | FP32.4  | QML Q               |

| 5962-0250101VXC                  | -55 to +125°C     | 40 ns | FP32.4  | QML V               |

| 5962R0250101VXC                  | -55 to +125℃      | 40ns  | FP32.4  | QML V RHA           |

| SMDJ-65609EV-40SCC               | -55 to +125°C     | 40 ns | FP32.4  | ESCC                |

| MM0 -65609EV-40-E <sup>(1)</sup> | 25°C              | 40 ns | Die     | Engineering Samples |

| MM0 -65609EV-40SV <sup>(1)</sup> | -55 to +125°C     | 40 ns | Die     | QML V               |

Note: 1. Contact Atmel for availability.

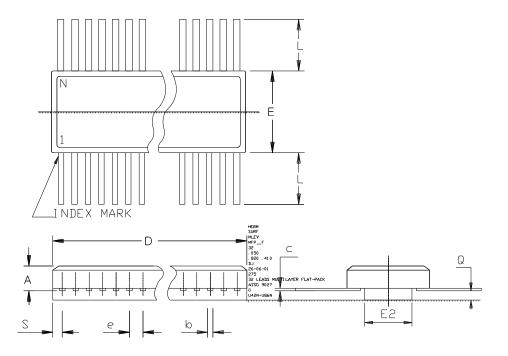

# **Package Drawing**

# 32-pin Flat Pack (400 Mils)

|    | ММ       |       | INCH     |        |

|----|----------|-------|----------|--------|

|    | Min      | Mα×   | Min      | Max    |

| А  | 1.78     | 2. 72 | . 070    | . 107  |

| b  | 0.38     | 0. 48 | . 015    | . 019  |

| С  | 0.076    | 0.15  | . 003    | . 007  |

| D  | 20. 62   | 21.03 | . 81 2   | . 828  |

| E  | 10.26    | 10.57 | . 404    | . 416  |

| E2 | 6. 96    | 7. 26 | . 274    | . 286  |

| е  | 1.27 BSC |       | .050 BSC |        |

| L  | 7. 37    | 7. 87 | . 290    | . 31 0 |

| Q  | 0. 51    | 0. 76 | . 020    | . 030  |

| S  |          | 1.14  |          | . 045  |

| N  | 32       |       | 32       |        |

### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131 Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

## **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland

Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369

### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

### **Atmel Operations**

### Memory

2325 Orchard Parkway San Jose, CA 95131 Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18

#### ASIC/ASSP/Smart Cards

Fax: (33) 2-40-18-19-60

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park

Maxwell Building

East Kilbride G75 0QR, Scotland

Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

### Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France

Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

### e-mail

literature@atmel.com

Web Site

http://www.atmel.com

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORYWAR-RANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULARPURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUTOF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes norepresentationsor warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications or product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for useas components in applications intended to support or sustainlife.

©2007 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, are the trademarks or registered trademarks, of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.